随着云计算和边缘计算的快速发展,数据处理器(DPU)作为数据中心的关键组件,其性能与能效比的需求日益凸显。

在第五届RISC-V中国峰会期间,翼华科技CTO胡昭明透露:“翼华科技作为一家专注于RISC-V架构的初创公司,正在通过自研RISC-V Core开发DPU产品,同时公司首款产品SmartNIC已成功流片并商用落地,这也是国内首款基于RISC-V的智能网卡产品。”

RISC-V在DPU中的技术优势

根据胡昭明的介绍,翼华科技选择RISC-V架构,主要基于其灵活性和快速市场响应的需求。

“尽管RISC-V生态相较于X86和ARM仍存在不足,但其在底层工具链(如GCC和LLVM)、网络层开源软件以及操作系统(如Linux、Ubuntu)的支持已相对成熟。” 胡昭明坦诚道。

具体来讲,DPU的核心功能是存储和计算卸载,而RISC-V指令集的灵活扩展性为满足高带宽、低延迟和能效比需求提供了独特优势。

在此基础上,翼华科技通过指令集扩展、微架构设计和软硬件协同三种手段实现了DPU的性能优化:

在指令集扩展方面,公司通过RISC-V的矢量扩展(Vector Extension)来支持批量加载/存储,单条指令即可完成多数据搬运,显著减少了指令开销。掩码访存技术能够仅处理有效数据(如稀疏矩阵运算),避免无效内存访问。此外,跨步和索引访存支持非连续数据模式,可有效提升带宽利用率。

在定制化指令与加速器控制方面,公司针对网络和存储的特殊需求,开发了加解密和计算加速指令(Customized Instructions Extensions),通过定制化指令高效控制加速器,进一步优化了性能。

在软硬件系统方面,公司通过优化的向量化库函数(如RVV优化的memcpy/memset)和零拷贝网络栈(DPDK/SPDK),实现了数据初始化和传输的高效处理。例如,利用DPDK的Vector指令扩展优化内存拷贝和CRC计算,显著提升了性能。

关于软硬件协同的具体实现,胡昭明补充道:“我们针对DPDK的优化包括利用Vector指令扩展提升内存拷贝性能,以及通过CRC指令加速校验计算。在存储领域,SPDK的优化则是通过RISC-V的A扩展指令减少队列指针更新延迟,利用V扩展指令批量处理完成队列,降低轮询开销。此外,我们还通过自定义中断控制器(如PLIC+CLINT)在低负载时切换为中断模式,进一步降低了功耗。”

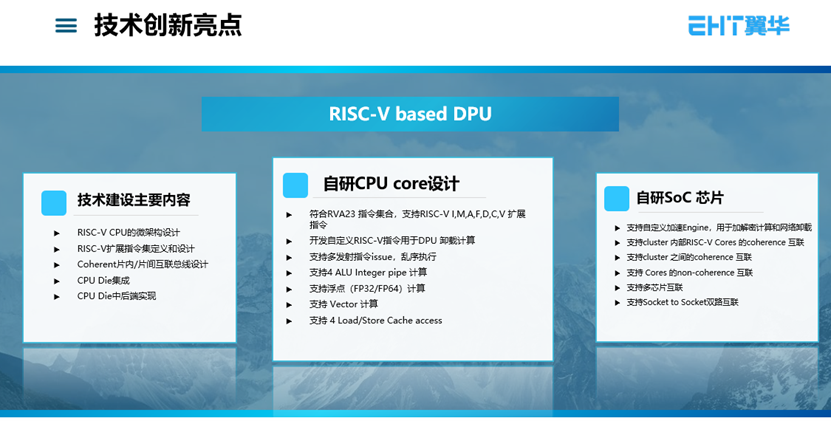

自研RISC-V 核与SoC设计

翼华科技在硬件设计上进行了创新,其自研RISC-V CPU核支持RVA23规范,具备多发射指令、乱序执行、浮点计算和矢量计算能力。核内设计包括4条ALU整数流水线、4条Load/Store流水线,以及高性能分支预测机制,能够满足高吞吐量计算需求。

此外,在SoC层面,翼华科技设计了灵活的集群架构:

- 每个Cluster最多支持4核,通过共享L2 Cache实现高效互联。

- 支持Cluster内和Cluster间的Coherent/Non-Coherent互联,以及多芯片片间互联。

- 通过高带宽总线连接自研加速引擎(如IPSec和网络卸载引擎),实现CPU与加速器的紧耦合,满足用户对性能、功耗和面积(PPA)的多样化需求。

写在最后

现阶段,翼华科技正在通过市场、技术、产品和生态的闭环驱动策略,培育网络和存储生态。同时,公司已经开发了特有的RDMA技术和P4技术,以及高性能计算核技术。

对此,胡昭明表示:“这种闭环模式不仅可以推动产品开发,还能通过开源社区反哺生态,进一步提升了RISC-V在网络和存储领域的成熟度。”

来源: 与非网,作者: 夏珍,原文链接: /article/1864624.html

芯耀

芯耀

3913

3913