名称:篮球比赛计分器设计VHDL代码Quartus? DE2-115开发板

软件:Quartus

语言:VHDL

代码功能:

基于FPGA的篮球比赛计分器

设计要求

1.系统主要外设:按键3个(自恢复式)、数码管1个,系统时钟(20kHz);

2.系统主要功能 三个按键分别为1分,2分,3分。当用户按下按键时,比赛队伍加上按键对应的分数,并且由数码管显示当前队伍得分。按下任意按键保持3秒,计数器清零。

备注:数码管为共阴极数码管要求。

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

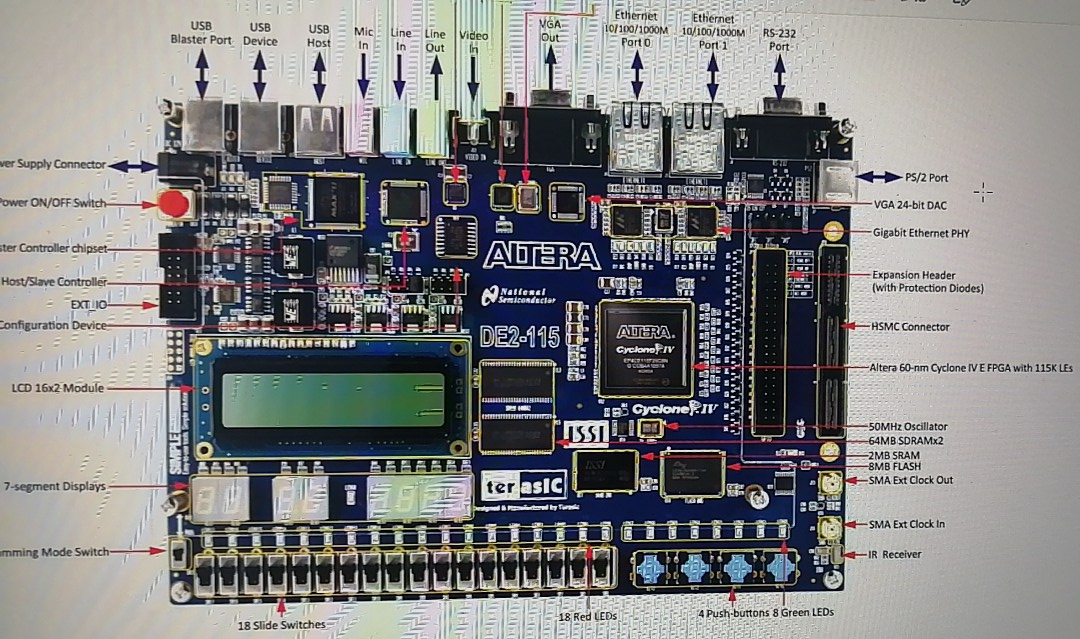

本代码已在DE2-115开发板验证,DE2-115开发板如下,其他开发板可以修改管脚适配:

演示视频:

设计文档:

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. 管脚分配

6. Testbench

7. 仿真图

整体仿真图

图中score_1和score_2是2队分数,s1,s2,s3控制加分,K1控制是1队加分还是2队加分

图中可以看到,k1=0时,给1队加分,可以加1,2,3分。k1=1时,给2队加分,可以加1,2,3分。

容易按键按下3秒,图中仿真了S3,长按后,分数清零

分数控制模块

显示模块

部分代码展示:

LIBRARY?ieee; USE?ieee.std_logic_1164.all;? LIBRARY?work; ENTITY?basketball_score?IS? PORT ( clk?:??IN??STD_LOGIC; K1?:??IN??STD_LOGIC; rst_n?:??IN??STD_LOGIC; S1?:??IN??STD_LOGIC; S2?:??IN??STD_LOGIC; S3?:??IN??STD_LOGIC; HEX0?:??OUT??STD_LOGIC_VECTOR(6?DOWNTO?0); HEX1?:??OUT??STD_LOGIC_VECTOR(6?DOWNTO?0); HEX2?:??OUT??STD_LOGIC_VECTOR(6?DOWNTO?0); HEX3?:??OUT??STD_LOGIC_VECTOR(6?DOWNTO?0) ); END?basketball_score; ARCHITECTURE?bdf_type?OF?basketball_score?IS? COMPONENT?score PORT(clk?:?IN?STD_LOGIC; ?K1?:?IN?STD_LOGIC; ?rst_n?:?IN?STD_LOGIC; ?S1?:?IN?STD_LOGIC; ?S2?:?IN?STD_LOGIC; ?S3?:?IN?STD_LOGIC; ?score_1_o?:?OUT?STD_LOGIC_VECTOR(7?DOWNTO?0); ?score_2_o?:?OUT?STD_LOGIC_VECTOR(7?DOWNTO?0) ); END?COMPONENT;

点击链接获取代码文件:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=1041

芯耀

芯耀

460

460